2019/07/27 - [전공/디지털회로] - CMOS(Complementary metal–oxide–semiconductor) Inverter

CMOS(Complementary metal–oxide–semiconductor) Inverter

Vin=0(LOW)일때 PMOS만 채널이 형성되고, Vout=VDD 값을 출력한다. Vin=VDD(HIGH)일때 NMOS만 채널이 형성되고, Vout=0 값을 출력한다. PMOS : Vth=-0.7, W=35u , L=1.1u, kp=20u (Body를 VDD에 연결) NMOS : V..

kwakd.tistory.com

CMOS로 Inverter 뿐만 아니라 NAND, NOR, AND, OR을 구현할 수 있다.

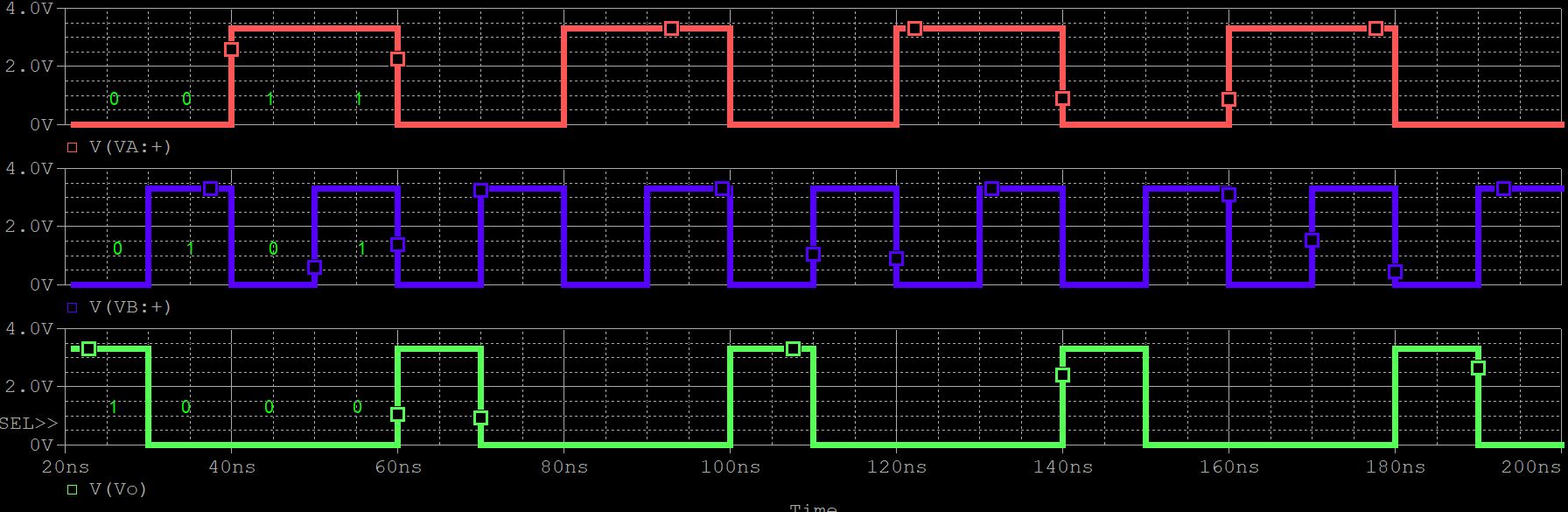

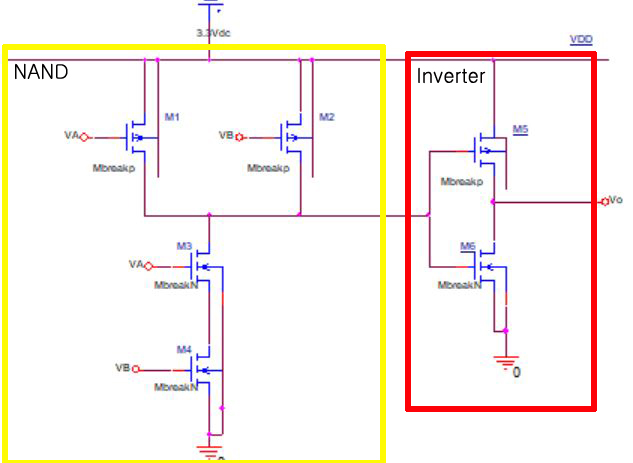

1) NAND

PMOS(M1,M2) : Vth=-0.7 W=35u L=1.1u kp=20u

NMOS(M3,M4) : Vth=0.7 W=10u L=1.1u kp=20u

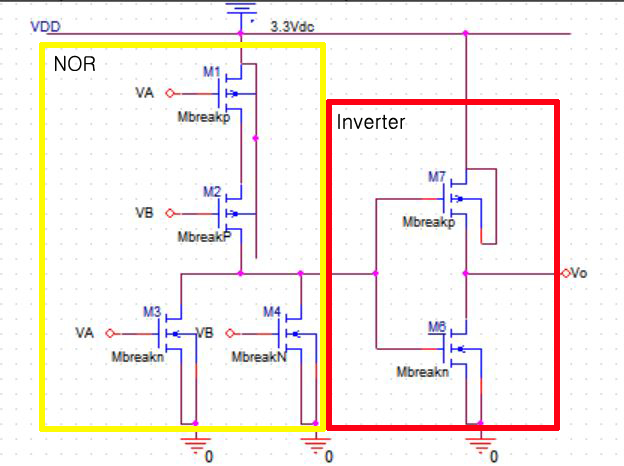

2)NOR

PMOS(M1,M2) : Vth=-0.7 W=35u L=1.1u kp=20u

NMOS(M3,M4) : Vth=0.7 W=10u L=1.1u kp=20u

3)AND

PMOS(M1,M2,M5) : Vth=-0.7 W=35u L=1.1u kp=20u

NMOS(M3,M4,M6) : Vth=0.7 W=10u L=1.1u kp=20u

4) OR

PMOS(M1,M2,M5) : Vth=-0.7 W=35u L=1.1u kp=20u

NMOS(M3,M4,M6) : Vth=0.7 W=10u L=1.1u kp=20u

결과적으로 NAND, NOR가 AND, OR보다 사용된 트랜지스터가 2개 적다. 따라서 NAND,NOR가 AND, OR보다 time delay가 더 작고 전력소모도 더 적을 수 밖에 없다. 그리고 2 input NAND, NOR의 input을 하나로 묶으면 inverter로도 사용가능하므로 NAND, NOR가 더 널리 쓰일 수 밖에 없다.

'전공 > 디지털회로' 카테고리의 다른 글

| CMOS(Complementary metal–oxide–semiconductor) Inverter (0) | 2019.07.27 |

|---|